引言

VME总线是一种性能优异、并行数据、实时性强、高可靠性且机械性能强的系统总线,可用于多CPU、数据的高速传送、高实时性的场合,基于其各方面优越的性能目前其在实时处理、工业控制机等诸多领域得到了广泛应用。

VME总线接口芯片在国外研究的已经比较成熟,但由于VME总线的结构复杂,在国内的研究还非常有限,目前我国国内通常使用Cypress的VIC64.CY7C964等专用芯片进行VME总线接口的设计,由于价格昂贵且不能根据系统要求灵活配置,使VME总线在工业控制系统的应用受到了限制。

超大规模集成电路技术的发展,尤其FPGA技术的发展,使得在一块可编程芯片上实现整个的嵌入式系统成为可能。FPGA可以快速成品,开发周期短,可修改程序中的错误且造价便宜,因此采用FPGA技术进行总线接口设计成为一种有效解决问题的新办法,有利于推动VME总线在工业控制中的广泛应用。

近些年来,工程技术的不断发展,推动了测量技术的不断革新。同时自动化控制系统的发展,对测量精度的要求越来越高,为满足这些设备的要求,用于测量的器件便将其分辨率提高。SSI接口有时钟和数据两个信号,通过串行方式来传输数据,简化了电路,降低了成本,提高了传输的可靠性。基于以上优点使得SSI接口在工业测量等领域得到了广泛应用。

本文采用FPGA作为核心芯片来采集处理SSI接口传输过来的数据,VME总线作为标准的数据交互接口,实现与上位机的数据交互。VME总线接口可以容纳多组从设备接口,不同的从设备配置不同的地址,主设备通过从设备的地址来实现对不同从设备的读取等操作,其可以方便的实现多组工业设备数据的读入,达到更准确的工业控制的目的。

一、硬件设计

在本文中选用Altera公司的CycloneⅡ系列FPGA中的性价比高的、有足够容量的EP2C8芯片。按照数据流方向描述,设计流程大致为:VME总线主控通过DTB将四路SSI接口的配置信息写入FPGA寄存器,FPGA按照配置信息输出四路时钟信号,经过电平和光耦之后加到磁致伸缩位移传感器上,磁致伸缩位移传感器在时钟信号的控制下送出位置信号,然后经过光耦和电平转换电路后输入FPGA,在FPGA中实现数据的串并转换、格雷码到二进制码的码制转换,经缓存处理后,按照主设备要求的方式将数据放到DTB,通过DTACK#信号通知主设备读取。

本设计硬件电路可以分为三大部分:一是SSI接口电路,包括光耦隔离电路和电平转换电路;二是FPGA控制系统电路,其由电源电路、时钟电路、配置电路、复位电路等组成;三是VME接口电路,这部分包括电平转换和数据方向控制电路。

SSI电路中选用双沟道集成的高速光耦HCPL0631作为核心隔离器件对SSI的时钟和数据信号做了隔离处理,由于光耦输出信号电平一般最小为4.5V,而输入FPGA的I/O口电压为3.3V,为了实现电平匹配,又对隔离后的信号进行了电平转换,芯片选用AD公司的ADG3301BRU。SSI协议中信号的传输符合RS422电平标准,其输出信号的高电平电压为5V,而从FPGA管脚输出的控制时钟信号为LVTTL电平,高电平电压为3.3V,为了实现信号互联,必须对SSI接口的控制时钟信号进行电平转换,由于有四路SSI接口信号,所以采用了MAXIM公司生产的MAX3030E芯片,该芯片恰好支持四路信号。

二、FPGA逻辑设计

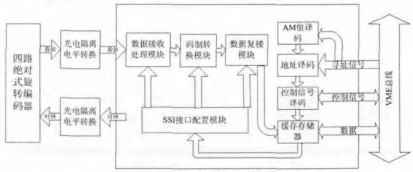

硬件电路主要用来完成数据的采集和传输工作,而数据的处理,总线控制等则通过FPGA内部的逻辑电路实现。FPGA里面的逻辑电路包含很多的模块,包括码制转换模块,数据处理模块等模块,各个模块相互协作来完成电路所要的功能,FPGA内部功能模块总体框架如图1所示:

数据处理模块实现了SSI接口协议,根据输入的数据字位宽,接收串行数据,同时实现数据的串并转换。在接收完一个完整的数据字以后,进入空闲时间,等待下一个数据传输周期。码制转换模块根据输入数据的编码方式决定是否进行码制转换。如果SSI数据的编码方式是格雷码,那么需要进行格雷码到二进制的转换;如果SSI数据的编码方式是二进制,则将输入的二进制码直接输出即可。数据复接模块接收四路数据输出模块的数据,根据通道选择码选择将四路数据中的某路数据输入数据缓存寄存器。

AM值译码模块是VME通信的开始,VME从设备不断扫描AS、IACK以及AM的值,当IACK为高电平,AS为低电平,AM值为0x39的时候,AMselecct信号则变为高电平;当其中一个条件不满足时,AMselecct信号为低电平。其中AM值为0x39时,表示VME总线的寻址方式为24位标准寻址。

地址译码模块用来对VME地址线进行译码,在AM值译码模块的输出AMselect的值为高电平时,启动地址译码工作,如果地址线给出的地址和接口板的地址一致,则地址译码输出Addselect为高电平,这种情况表示接口板被选中,可以和上位机进行通信了。总线主控驱动A01-A31、AM0-AM5、IACK*、LWORD*寻址目标,在AS*下降沿有效。总线主控还要驱动WRITE*为高以完成读操作,也要将DS0*、DS1*驱动为低。目标对地址译码后,确认寻址的是自己,就将数据放入D00-D31.并驱动DTACK*到低。如果总线出错,则驱动BERR*到低。

三、系统测试

本文在测试中,使用的是接口板的第四路通道,编码器为西门子的6FX2001-5FS12磁致伸缩位移传感器,输出的数据为十二位的格雷码,波特率采用500KHz,要写入的配置数据为0xf843(保留位都取为高电平),拨码开关输入的地址位为0x1000.板卡的基地址为0x100000.要读的数据通道地址为0x10000c,测试实现了主机通过VME总线对板卡SSI通道的配置及对磁致伸缩位移传感器输出数据的正确读取,达到了本文初衷。图2为主控从接口板上读取过来的数据波形。

四、结论

该板卡是VME总线的一个3U规格的从设备,完成了主控对SSI通道的配置和数据的传输。本设计的难点在于使用FPGA芯片来实现VME总线协议和SSI接口协议,并完成数据的采集处理和传输。该接口板使用FPGA来实现对VME总线的控制,比起使用专用集成芯片来控制VME总线更有优势,它降低了接口板的设计成本并且提高了其灵活性。为VME总线接口电路设计提供了一个新的思路与方向。

微信扫一扫

微信扫一扫